很容易驗證間隙,高速,制造的約束,并通過計算最大的焊盤和可測試性極限。建立、保存和使用驗證方案。只有兩次鼠標點擊,違規(guī)行為才能以直觀的形式發(fā)生。自動從電子表格中選擇一個沖突,以放大和更正該沖突,并快速重新驗證已修復該沖突。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

計算

+關注

關注

2文章

439瀏覽量

38671 -

PADS

+關注

關注

79文章

807瀏覽量

107558 -

焊盤

+關注

關注

6文章

539瀏覽量

38013

發(fā)布評論請先 登錄

相關推薦

電路的兩類約束指的是哪兩類

電路的兩類約束通常指的是電氣約束和物理約束。這兩類約束在電路設計和分析中起著至關重要的作用。 一、電氣約束 電氣

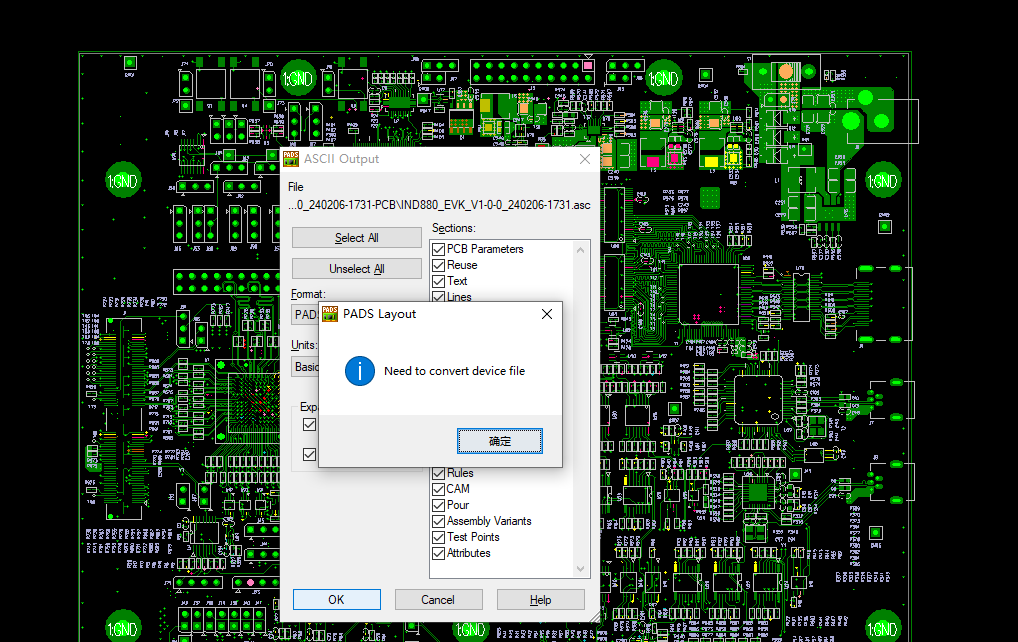

pads閃退故障解決方案 PADS報Need to convert device file然后Open error:devices.dat確定閃退

PADS 報Need to convert device file, 然后Open error:devices.dat 確定閃退

時序約束實操

添加約束的目的是為了告訴FPGA你的設計指標及運行情況。在上面的生成約束之后,在Result àxx.sdc中提供約束參考(請注意該文件不能直接添加到工程中,需要熱復制到別的指定目錄或者新建自己的SDC文件添加到工程)。

Xilinx FPGA的約束設置基礎

LOC約束是FPGA設計中最基本的布局約束和綜合約束,能夠定義基本設計單元在FPGA芯片中的位置,可實現(xiàn)絕對定位、范圍定位以及區(qū)域定位。

發(fā)表于 04-26 17:05

?962次閱讀

pads轉cad詳細步驟

將PADS轉換為CAD是一種常見的工程需求,因為PADS是一種PCB設計軟件,而CAD軟件(如AutoCAD)通常用于產生更多種類的設計文件。在下面的文章中,我將為您提供將PADS轉換為CAD的詳細

FPGA物理約束之布局約束

在進行布局約束前,通常會對現(xiàn)有設計進行設計實現(xiàn)(Implementation)編譯。在完成第一次設計實現(xiàn)編譯后,工程設計通常會不斷更新迭代,此時對于設計中一些固定不變的邏輯,設計者希望它們的編譯結果

pads如何使用自動布線功能

自動布線是現(xiàn)代電子設計中非常重要的一環(huán),它可以幫助電路設計師快速完成PCB布局設計并提高產品性能。pads作為一款專業(yè)的電路設計軟件,提供了強大的自動布線功能,能夠以速度和效率較高的方式完成電路路徑

CAD圖如何導入到PADS里及出現(xiàn)的問題

電子發(fā)燒友網站提供《CAD圖如何導入到PADS里及出現(xiàn)的問題.pdf》資料免費下載

發(fā)表于 12-18 10:59

?1次下載

FPGA物理約束之布線約束

IS_ROUTE_FIXED命令用于指定網絡的所有布線進行固定約束。進入Implemented頁面后,Netlist窗口如圖1所示,其中Nets文件展開后可以看到工程中所有的布線網絡。

PADS教程:原理圖創(chuàng)建過程

PADS教程系列,專門用來分享對于PADS的設計使用,會定期更新,喜歡的可以收藏,PADS教程系列會統(tǒng)一整理在公眾號菜單欄,有需要可以移步菜單欄進行查看。 在電子設計中,EDA軟件那是必不可少的,像

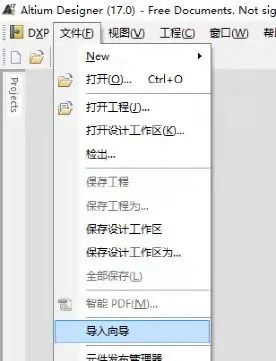

PADS文件如何轉Altium Designer文件

在電子硬件設計中,常常用用到3款EDA設計軟件:Altium Designer, Pads, cadence。 Altium Designer: 在高校中使用非常普遍(相信很多硬件工程師接觸的第一款

PADS的視覺約束驗證

PADS的視覺約束驗證

評論