聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關(guān)注

關(guān)注

1624文章

21539瀏覽量

600483 -

Altera

+關(guān)注

關(guān)注

37文章

774瀏覽量

153769 -

數(shù)碼管

+關(guān)注

關(guān)注

32文章

1871瀏覽量

90727 -

DIY

+關(guān)注

關(guān)注

176文章

885瀏覽量

347835

發(fā)布評論請先 登錄

相關(guān)推薦

如何實現(xiàn)數(shù)碼管動態(tài)顯示

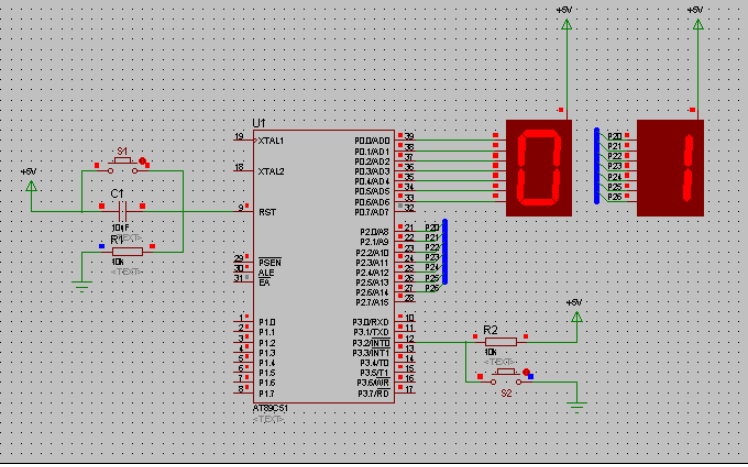

實現(xiàn)功能:按下按鍵時,數(shù)碼管動態(tài)顯示‘ 鍵值-掃描值 ’按鍵松開時,數(shù)碼管動態(tài)顯示‘ 0-00

發(fā)表于 01-07 06:22

完成數(shù)碼管動態(tài)顯示的方法

開拓者FPGA開發(fā)板上有六個共陽極八段數(shù)碼管,本實驗將完成數(shù)碼管動態(tài)顯示。數(shù)碼管動態(tài)/靜態(tài)

發(fā)表于 01-18 10:25

分享三個在FPGA開發(fā)板上實現(xiàn)數(shù)碼管動態(tài)顯示的案例

1、在FPGA開發(fā)板上實現(xiàn)數(shù)碼管動態(tài)顯示的案例介紹數(shù)碼管動態(tài)顯示原理在開展本章實驗之前,我們需要

發(fā)表于 07-25 15:18

分享一個基本的數(shù)碼管動態(tài)顯示案例

穩(wěn)定地顯示各自的圖案。在上個鏈接的文章,即介紹模塊化設計的文章中,有一個實例是利用撥碼開關(guān)手動地控制數(shù)碼管的位選。而在實現(xiàn)數(shù)碼管

發(fā)表于 08-01 15:21

數(shù)碼管(動態(tài)顯示)【C語言版】

數(shù)碼管(動態(tài)顯示)【C語言版】數(shù)碼管(動態(tài)顯示)【C語言版】數(shù)碼管(動態(tài)顯示)【C語言版】

發(fā)表于 12-29 15:51

?0次下載

采用FPGA DIYK開發(fā)板控制模為60的計數(shù)器數(shù)碼管動態(tài)顯示

FPGA diy作業(yè)實現(xiàn)模為60的計數(shù)器數(shù)碼管動態(tài)顯示。

利用FPGA DIY開發(fā)板實現(xiàn)撥碼開關(guān)控制靜態(tài)數(shù)碼管顯示

FPGA diy作業(yè)實現(xiàn)撥碼開關(guān)控制顯示數(shù)碼管0到8的靜態(tài)顯

采用FPGA DIY開發(fā)板實現(xiàn)數(shù)碼管動態(tài)顯示60計數(shù)

asean的 FPGA DIY 數(shù)碼管動態(tài)顯示60計數(shù)視頻

FPGA入門系列實驗教程之使用FPGA實現(xiàn)數(shù)碼管動態(tài)顯示的資料免費下載

實現(xiàn)開發(fā)板上 8 個數(shù)碼管動態(tài)顯示 0~7。通過這個實驗,掌握采用 Verilog HDL語言編程實現(xiàn) 7 段數(shù)碼管

發(fā)表于 06-12 16:32

?15次下載

數(shù)碼管動態(tài)顯示的原理概述

動態(tài)顯示的特點是將所有數(shù)碼管的段選線并聯(lián)在一起,由位選線控制是哪一位數(shù)碼管有效。選亮數(shù)碼管采用動態(tài)

發(fā)表于 11-04 08:00

?0次下載

使用FPGA DIY控制板實現(xiàn)數(shù)碼管動態(tài)顯示功能

使用FPGA DIY控制板實現(xiàn)數(shù)碼管動態(tài)顯示功能

評論